# REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE Ministère de l'Enseignement Supérieure et de la Recherche Scientifique

Université Djilali Bounaâma de Khemis Miliana

Niveau: 1ère année MI matière: Structure machine II

## Série de TD N°2(Circuits Combinatoires)

#### **Exercice N°1:**

Un comparateur n bits est un circuit servant à comparer 2 mots  $(A_0A_1 \dots A_{n-1})$  et  $(B_0B_1 \dots B_{n-1})$  de n bits chacun. La sortie vaut 1 si les mots sont identiques et 0 sinon.

- 1. Réaliser un comparateur 1 bit.

- 2. En déduire le circuit du comparateur 4 bits.

#### **Exercice N°2:**

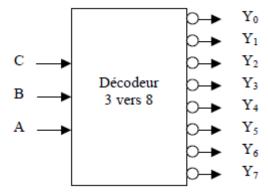

On souhaite faire la synthèse d'un décodeur 3 vers 8 avec les sorties actives au niveau bas.

- 1-Etablir la table de vérité du circuit.

- 2-Déterminer les fonctions de sorties Yi=f(A,B,C)

- 3-Donner une implantation avec des portes NAND

- 4-Comment faut-il modifier le schéma pour ajouter au circuit une entrée de validation  $\overline{V}\;$  telle que le circuit fonctionne normalement quand  $\overline{V}=1$  et que toutes les sorties  $Y_i=1$  quand  $\overline{V}=0$  ?

#### **Exercice N°3:**

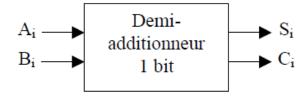

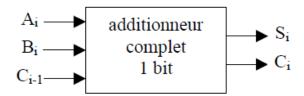

On cherche à réaliser un circuit permettant d'effectuer l'addition ou la soustraction sur 1 bit avec retenue entrante

1-établir la table de vérité et le schéma du demi-additionneur qui effectue l'opération  $S_i = A_i + B_i$  et qui calcule la retenue sortante.

2-En déduire la table de vérité et le schéma de l'additionneur complet qui effectue l'opération  $S_i = A_i + B_i + C_{i-1}$  et qui calcule la retenue sortante.

3-même questions 1 et 2 pour le soustracteur.

4-en comparant l'étage additionneur et l'étage soustracteur 1 bit, proposer un montage unique qui, à l'aide d'une commande externe permet de réaliser soit l'addition, soit la soustraction.

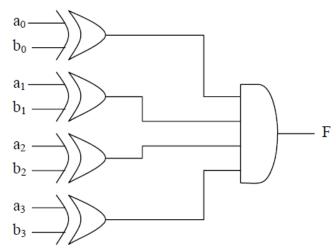

### **Exercice N°4:**

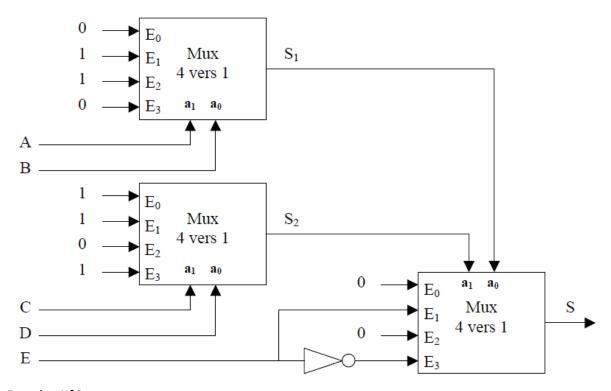

Analyser le circuit ci-dessous et définir son rôle

## **Exercice N°5:**

Donner l'équation logique S=f(A,B,C,D,E) du circuit suivant :

## Exercice N°6:

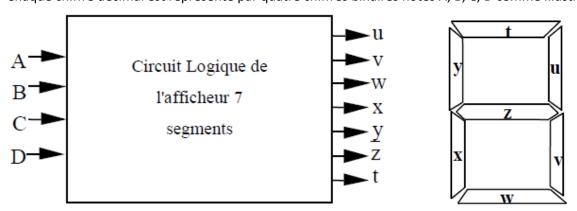

L'afficheur 7 segments permet de présenter les nombres décimaux à partir de leur code BCD (Binary Coded Decimal). Chaque chiffre décimal est représenté par quatre chiffres binaires notés A, B, C, D comme illustré par la figure suivante.

- 1. Donner la table de vérité de l'afficheur 7 segments.

- 2. Simplifier par la méthode algébrique ou la méthode graphique les expressions des différentes sorties.

- 3. Donner le logigramme de l'afficheur 7 segments.

#### **Exercice N°7:**

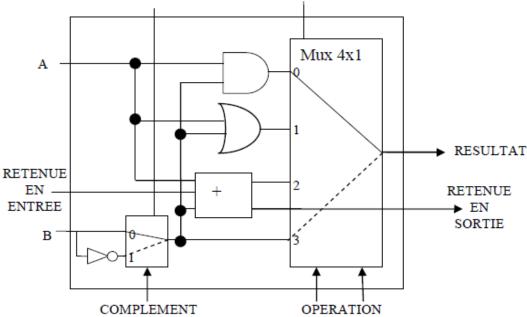

Le logigramme de la figure suivante est une unité arithmétique et logique de taille 1 bit. Sur ce circuit, on dispose de deux multiplexeurs :

- le premier a 4 entrées sélectionnées par OPÉRATION. Selon l'entrée OPÉRATION, on obtient en résultat le produit logique de A et B, la somme logique de A ou B, l'addition arithmétique de A à B, et enfin, l'entrée B ou son complément.

- le deuxième a deux entrées sélectionnée par COMPLÉMENT permettant de complémenter à souhait l'entrée B

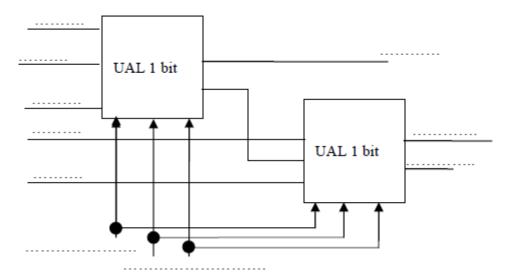

- **1.** Compléter le circuit de la figure suivante de sorte à obtenir une unité arithmétique et logique 2bits. Placer pour répondre sur la figure ci-dessous :

- Les lignes de sélection OPÉRATION et COMPLÉMENT.

- les entrées du circuit : Ao, A1, Bo, B1, Re où Re est la retenue en entrée

- les sorties : So, S1 et Rs où Rs est la retenue en sortie.

2. Proposer une approche permettant de réaliser la soustraction de B à A. Justifier votre réponse.

#### **Exercice N°8:**

Un système reçoit, codés en binaire naturel, des nombres compris entre 0 et 20 (inclus). Les digits d'entrée sont par poids d'ordre croissant A, B, C, D et E. Le système délivre trois informations S, T et U :

- •La sortie S vaut 1 lorsqu'un nombre divisible par trois se présente à l'entrée.

- •La sortie T vaut 1 lorsqu'un nombre divisible par cinq se présente à l'entrée.

- •La sortie U vaut 1 lorsqu'un nombre divisible par sept se présente à l'entrée.

- 1. donner le schéma symbolique de ce système.

- 2. Donner la table de vérité du système.

- 3. Simplifier les équations logiques à l'aide des tableaux de Karnaugh.

- 4. Réaliser les fonctions T et U à l'aide de portes NAND.

- 5. Réaliser les fonctions S, T, U à l'aide de multiplexeurs 16 entrées.